IT之家 4 月 19 日消息,爆料人 Jaykihn 再次透露了关于英特尔下一代酷睿 Ultra 400 系列桌面处理器 Nova Lake-S 的更多细节。

首先,Nova Lake-S 将按核心数量分为三大层级,而且带 bLLC 大缓存的处理器将采用新的 D/DX 后缀命名:

22 核型号(6P+12E+4LPE)没有后缀,与不带 bLLC 的高端型号同属于经典酷睿 Ultra 9 系列

24 核(8+12+4)和 28 核(8+16+4)型号属于 D 系列,分别为 Ultra 7 和 Ultra 9 层级,将以酷睿 Ultra 7/9 400D 为名上市

44 核(16+24+4)和 52 核(16+32+4)型号属于 DX 系列,超脱于 Ultra 层级之外。

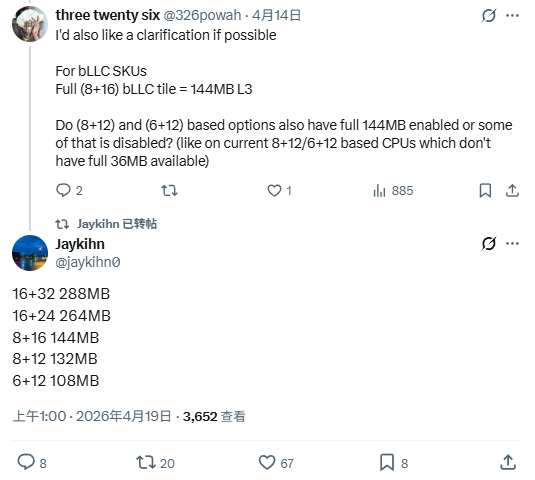

如此前爆料,该系列 CPU 将提供部分配备 bLLC(Big Last Level Cache,大容量末级缓存)的型号,旗舰型号将提供最高 288MB 的总缓存容量,相比 AMD R9 9950X3D2 高出 80MB(约 38%)。

当然,关于 288MB 型号的爆料此前早已传出。但除此之外,Nova Lake-S 桌面处理器还将包含四种主要芯片(Die)配置。

Nova Lake-S 双计算模块版本被标注为“DS”,面向发烧友市场。其中,定位最高的 52 核型号(两块 8P+16E 芯片再加 4LPE)将配备两片 144MB 的 bLLC 缓存,即 288MB;44 核型号(两块 8P+12E 芯片再加 4LPE)也将提供 264MB 的缓存容量。

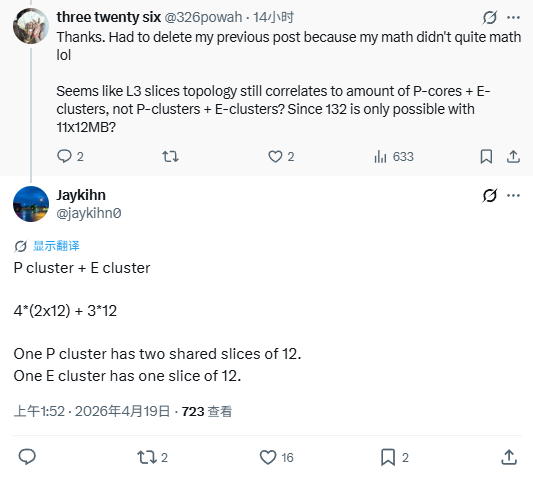

在单计算模块产品线中,28 核型号(8P+16E+4LPE)将配备 144MB 缓存,24 核型号(8P+12E+4LPE)则为 132MB,22 核型号(8P+10E+4LPE)为 108MB。以 132MB 型号为例,其中 P 核簇含有 4 片双 12MB 缓存芯片、E 核簇含有 3 片 12MB 缓存芯片。

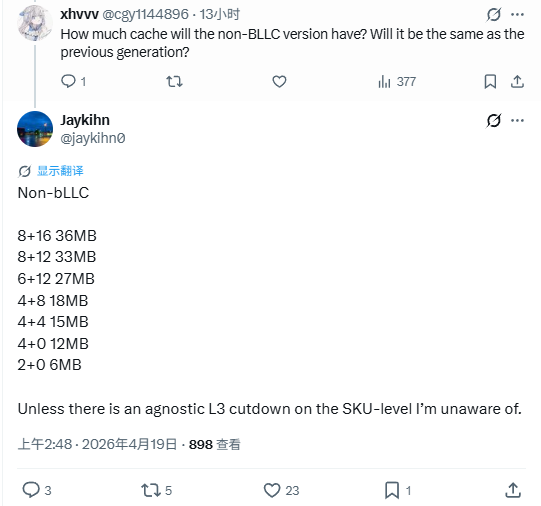

对于标准版(无 bLLC 缓存)而言,最大仍配备 36MB 高速缓存:

28 核型号(8P+16E+4LPE)将配备 36MB 三级缓存

24 核型号(8P+12E+4LPE)为 33MB

22 核型号(6P+12E+4LPE)为 27MB

16 核型号(4+8+4)为 18MB

12 核型号(4+4+4)为 15MB

8 核型号(4+0+4)为 12MB

6 核型号(2+0+4)为 6MB。

Jaykihn 还指出,虽然 Nova Lake-S 最高可提供 52 核型号,但该系列处理器仍为消费级定位,并不包含传统意义上的 SMT(超线程)或 HEDT 产品。

其他方面,Nova Lake-S 将采用全新 LGA 1954 插槽,采用 Coyote Cove(P 核)+ Arctic Wolf (E/LPE 核)架构,支持 AVX10.2 指令集,不会提供超线程版本,标配 2 个 Xe3 核显,支持 8000 MT/s 内存,支持 ECC、CUDIMM、CSODIMM 内存特性,配备 74 TOPS NPU,支持雷电 5 及 Wi-Fi 7,提供 24 条 PCIe Gen5 通道,功耗最高可达 350~700W,预计 CES 2027 前发布。

| ID | 核心数 | 核心配置 | 缓存 | TDP/cTDP | ||

|---|---|---|---|---|---|---|

| ? | P3DX | 52 | 2x(8P+16E)+4LPE | bLLC | 288 MB | 175W |

| ? | P2DX | 44 | 2x(8P+12E)+4LPE | bLLC | 264 MB | 175W |

| Ultra 9 | P2D | 28 | 8P+16E+4LPE | bLLC | 144 MB | 125W |

| Ultra 9 | P2K | 28 | 8P+16E+4LPE | / | 36MB | 125W/65W |

| Ultra 9 | P2 | 22 | 6P+12E+4LPE | bLLC | 108 MB | 65W |

| Ultra 7 | P1D | 24 | 8P+12E+4LPE | bLLC | 132 MB | 125W |

| Ultra 7 | P1K | 24 | 8P+12E+4LPE | / | 33MB | 125W/65W |

| Ultra 7 | P1 | 16 | 4P+8E+4LPE | / | 18MB | 65W/35W |

| Ultra 5 | MS2K/MS2KF | 22 | 6P+12E+4LPE | / | 27MB | 125W/65W |

| Ultra 5 | MS2 | 12 | 4P+4E+4LPE | / | 15MB | 65W/35W |

| Ultra 5 | MS1 | 8 | 4P+0E+4LPE | / | 12MB | 65W/35W |

| Ultra 3 | T1 | 6 | 2P+0E+4LPE | / | 6MB | 65W/35W |

IT之家注:bLLC 技术是英特尔针对 AMD 3D V-Cache 技术推出的应对方案,但两者实现路径不同,英特尔的 bLLC 并未采用 AMD 的 3D 堆叠技术,而是将大容量缓存直接集成在计算模块内,靠芯片面积硬换性能,所以单芯片面积远超 AMD。

除了大缓存版本,英特尔届时还将推出大核显版本(可能不仅限于移动平台),预计将命名为 Nova Lake-AX 系列,采用 LGA 4326 巨型插槽,提供最多 48 个 Xe 核心。

相关阅读:

《英特尔 "Nova Lake S" 处理器确认归属第四代酷睿 Ultra,2026Q4 量产》

《英特尔 Nova Lake 处理器尺寸曝光:单芯片面积远超 AMD,采用台积电代工》

《英特尔 Nova Lake-AX 曝光:LGA 4326 巨型插槽,48 个 Xe 核心》

《曝英特尔 "Nova Lake" 处理器采用 Xe3 / Xe3P GPU IP,AX 高阶变体取消》

《英特尔 Nova Lake 处理器 Xe3P 架构核显性能被曝比 Xe3 提升 20~25%》