1.一场打了两年的“空气诉讼”:英诺赛科赢下ITC终裁;

2.西安交大王莉团队提出SDREC策略实现可编程可擦写微结构阵列高精度打印;

3.西安电子科技大学梁鸿志等在2026年JSSC发表高能效8位32GS/s高度数字化模数转换器芯片成果;

4.合肥工业大学在锑基光电子器件研究中取得重要进展

1.一场打了两年的“空气诉讼”:英诺赛科赢下ITC终裁

2026 年 5 月 8 日 —— 英诺赛科今日宣布,美国国际贸易委员会(“ITC”)在第 337-TA-1414 号调查中作出最终裁定,确认英诺赛科当前的氮化镓(“GaN”)功率器件产品未侵犯英飞凌的相关专利,并可不受限制地继续在美国进口和销售。

ITC 全体委员一致同意英诺赛科现有产品未侵犯英飞凌的美国第 9,070,755 号专利(涉及电极设计)和第 9,899,481 号专利(涉及封装设计)。

委员会仅认定 第 9,899,481 号专利中的两项权利要求有效且仅被英诺赛科早已停止生产和销售的历史旧产品侵权。因此,相关的进口和销售禁令对英诺赛科在美国的现有业务不具有实质影响。英诺赛科将继续不间断地向美国及全球客户供应其现有的 GaN 功率产品。

ITC 的最终裁定确认,英诺赛科的产品源于独立自主的技术创新,并彻底挫败了英飞凌试图通过缺乏根据的诉讼手段限制合法竞争的企图。功率半导体行业的未来应由更优异的产品所塑造,而非毫无根据的诉讼伎俩。英飞凌最终输掉了这场打了两年的“空气诉讼”。

2.西安交大王莉团队提出SDREC策略实现可编程可擦写微结构阵列高精度打印

微结构阵列因其在柔性电子、光学器件与生物传感等领域的广泛应用而备受关注,但传统制备往往依赖光刻等高成本、流程复杂的工艺,且图案更新与功能重构能力有限。

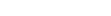

近日,西安交通大学机械工程学院王莉团队在荷电微液滴可控沉积与微结构阵列可重构制造方面取得新进展。研究团队提出一种基于残留电荷诱导电场调控的荷电液滴选择性沉积方法(Selective Deposition of Charged Droplets via Residual-Charge-Induced Electric Field Control, SDREC),实现了微结构阵列的可编程图案化构建与“擦除—重写”式可逆制造。

图1 论文信息

研究团队针对静电雾化/电流体沉积过程中“残留电荷会扰动后续液滴轨迹、影响沉积精度”的共性难题,反向利用残留电荷对局部电场的调制作用:通过电极图案与电场边界条件设计,使带电微液滴在飞行与落点阶段受到可控的电场牵引/排斥,实现对“该落在哪里、落多少、落成什么形貌”的选择性调控,从而将原本不利于成形的残留电荷效应转化为“可编程图案化”的关键驱动力。

图2 SDREC工作原理示意图

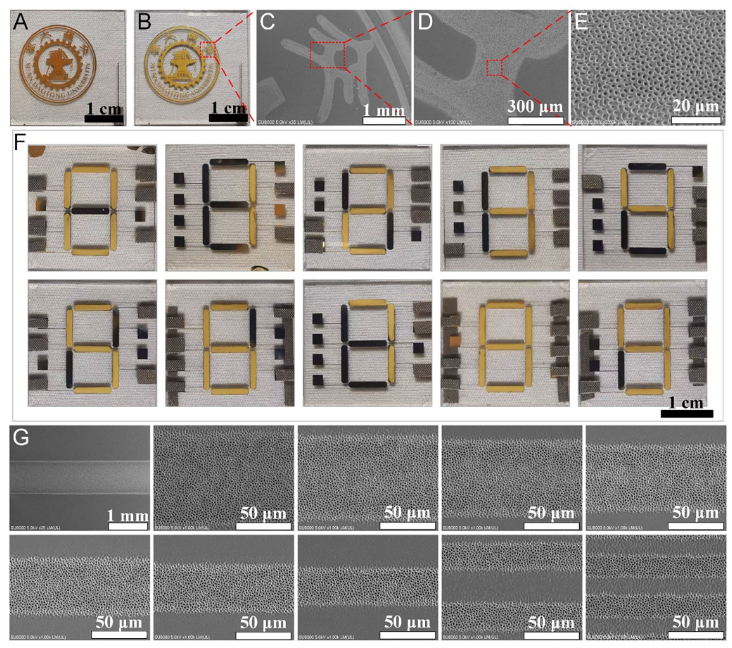

在实验验证中,团队在蚕丝蛋白表面实现了高分辨率图案化微结构阵列制备:选择性沉积形成的蜂窝状多孔微结构可复现校徽等复杂图形;同时通过线阵列分辨率测试,图案特征宽度可从毫米级进一步推进至20 µm量级,为高精度、低成本的微结构制造提供了新路径。

图3 基于SDREC的图案化微结构制备

作为概念验证,研究团队构建了可编程5×5像素阵列,并展示了图案的擦除与重写能力:图案不再一次成型、不可更改,而是可以在同一基底上进行多次更新与重构。

图4 图形化微结构的可编程、可擦除、可重写制备

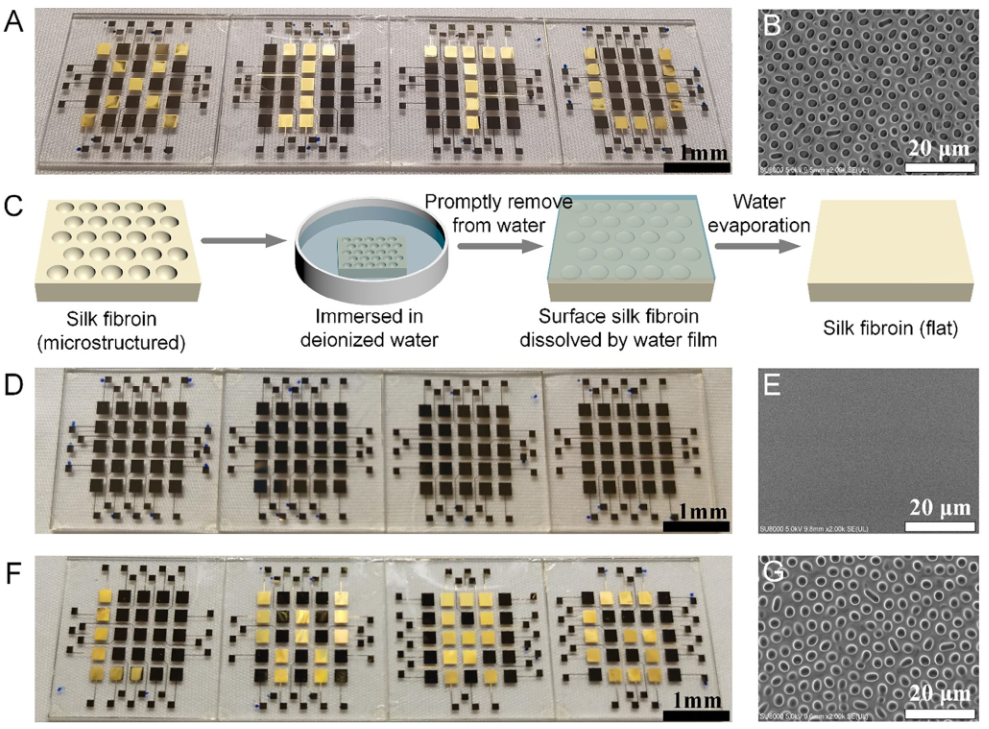

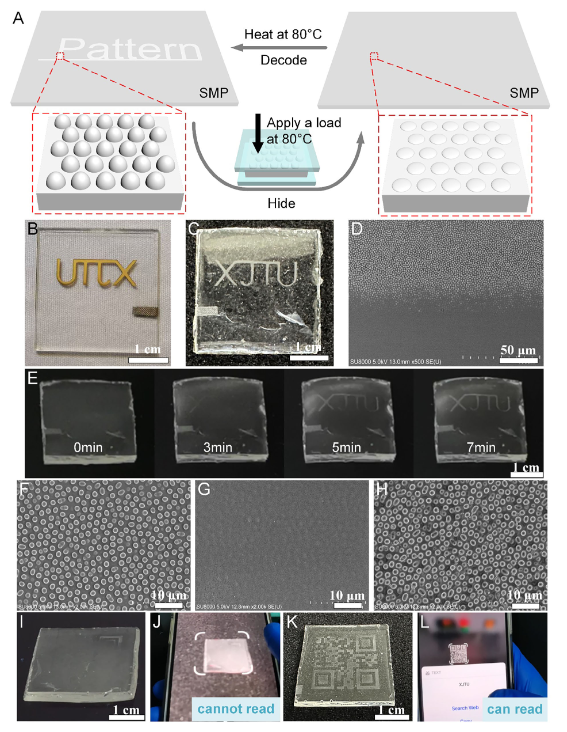

在可重构制造之外,该工作进一步将图案化微结构阵列转移至形状记忆聚合物上,实现了信息存储以及光学加密/解密展示。这为微结构阵列从“形貌构建”拓展到“信息功能器件”提供了新的应用方向,面向柔性光学防伪、可穿戴信息载体等场景具有潜在价值。

图5 利用图形化微结构阵列进行信息存储和加密

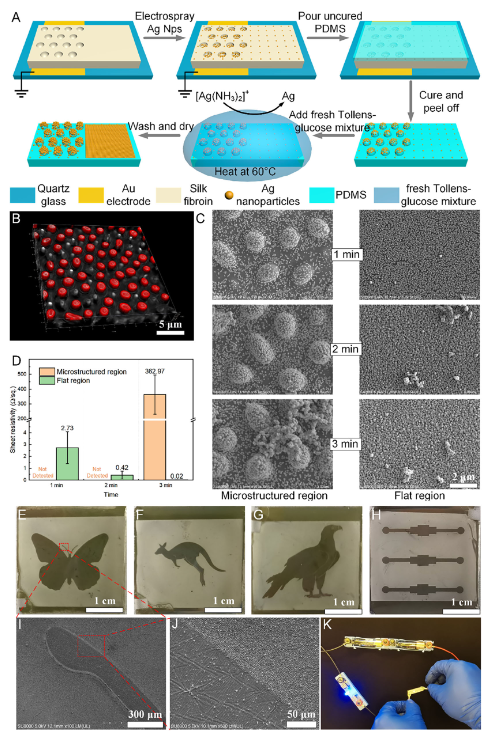

面向器件化应用,研究团队还在图案区域预沉积银纳米颗粒,并在此基础上实现了银电极的构建,展示了SDREC在“结构—功能”一体化制造中的拓展潜力,为柔性电子与图案化电极制备提供了新思路。

图6 图形化银电极制备

该研究为面向柔性电子、光学调控与生物传感等应用的高精度微结构阵列制造提供了具备重构能力的新型工艺思路:在避免复杂掩膜与多步光刻的同时,通过电场与残留电荷的协同调控实现图案快速迭代与功能扩展,为快速构建高精度微结构器件提供了可借鉴的技术路线。

相关成果以Selective Deposition of Charged Droplets for Programmable and Rewritable Printing of Patterned Microstructure Arrays为题在Advanced Science在线发表,机械工程学院博士生裴跃琛为论文第一作者,王莉副教授是共同第一作者兼通讯作者。

西安交通大学机械工程学院王莉团队长期从事电流体3D打印研究,已建立较为成熟的装备平台、工艺方法与材料体系,并在电流体打印中实现剪切取向可控排列的一维微纳材料方面积累了系统经验,相关成果作为封面文章(DOI: 10.1126/sciadv.adk3854) 与ACS Applied Materials & Interfaces(DOI: 10.1021/acsami.2c09672)发表。同时,团队通过电场调控引导液滴沉积,开发了电雾化“水刻蚀”新方法,实现微纳尺度准周期孔状结构的可图案化制备发表在Nano Energy(DOI: 10.1016/j.nanoen.2020.104974)。

课题组在中国工程院院士卢秉恒领导下的西安交通大学先进制造技术研究所工作,研究围绕微流体行为调控的增材制造及相关应用场景展开,应用范围在高精度3D打印等领域,涉及的工艺有压电微喷3D打印、高精度EHD打印、快速无层面曝光打印等,涉及的材料包含金属、非金属有机、无机、高分子等。研究范围包括基于深度学习的3D打印、微纳制造、软体机器人及电子/微电子打印与光电子器件制造、3D打印结构功能创新设计应用等。

论文链接地址:https://advanced.onlinelibrary.wiley.com/doi/10.1002/advs.202522210

王莉副教授课题组主页:https://gr.xjtu.edu.cn/en/web/wanglime

3.西安电子科技大学梁鸿志等在2026年JSSC发表高能效8位32GS/s高度数字化模数转换器芯片成果

西安电子科技大学模拟集成电路重点实验室梁鸿志、朱樟明团队在高能效8位32GS/s高度数字化模数转换器(ADC)芯片方向取得重要进展。团队基于28nm CMOS工艺提出了一款高能效8位32GS/s混合域架构时序交织ADC芯片,针对传统时间域ADC在PVT波动下性能不稳定的问题,采用多种自适应校准机制以提升系统鲁棒性;通过提高单通道采样速率、减少交织通道数量,从源头上缓解通道失配影响,并进一步降低系统复杂度与功耗开销,适用于超大规模数据中心、云计算平台及高速串行接口系统等应用场景。相关成果发表在2026年《IEEE Journal of Solid-State Circuits》(JSSC),论文题目为" A 16× Interleaved 32-GS/s 8b Hybrid ADC With Self-Tracking Inter-Stage Gain Achieving 44.3-dB SFDR at 20.9-GHz Input"(DOI: 10.1109/JSSC.2026.3680919)。论文第一作者为西安电子科技大学梁鸿志,第一学生作者为常军,共同通讯作者为西安电子科技大学朱樟明、刘术彬、沈易、李登全。

论文链接

https://ieeexplore.ieee.org/document/11482810

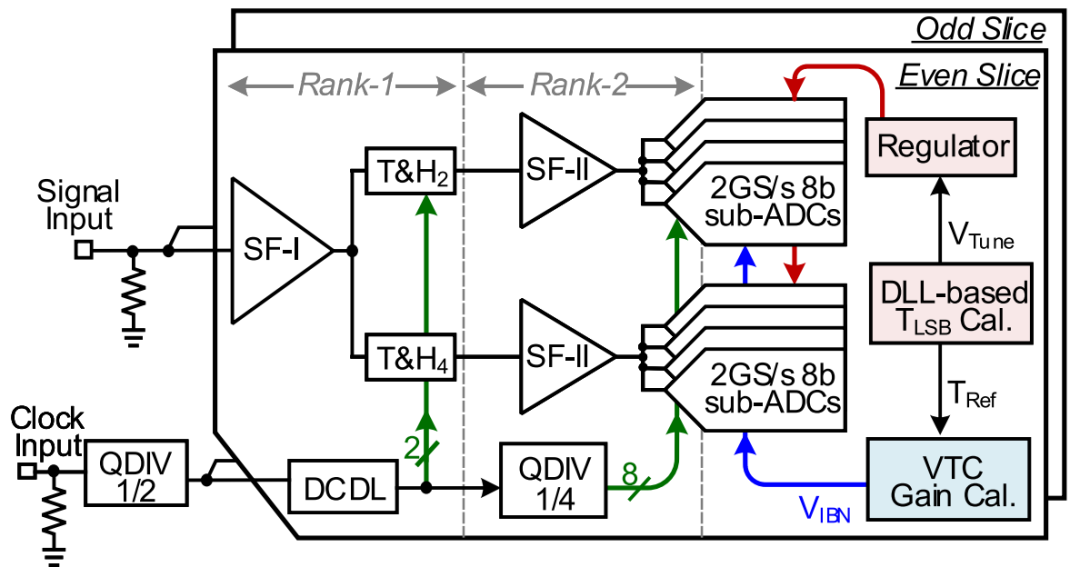

该工作提出了基于延时锁相环的量化范围自跟踪校准技术,通过构建与子ADC一致的延时复制链,实现对时间量化步长及满量程范围的实时跟踪与补偿,从根本上抑制PVT变化对系统精度的影响;引入模拟域自跟踪级间增益校准环路,通过电压-时间转换复制结构实现级间增益的自适应调节,有效解决了传统结构中级间增益失配对线性度和动态性能的制约;通过在前端引入逐次逼近辅助粗量化并嵌入失调校准机制,在降低后端时间量化精度要求的同时,实现了通道间失调误差的高效抑制,避免了复杂数字校准带来的额外硬件开销。

图1 高度数字化混合域交织ADC系统架构

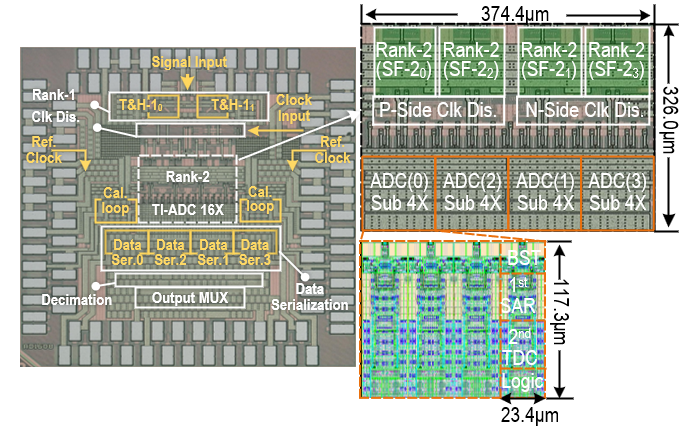

测试结果表明,该芯片在32 GS/s采样速率下,在奈奎斯特输入条件下实现了36 dB的SNDR和50.8 dB的SFDR;在20.9 GHz高频输入信号下仍保持44.3 dB的SFDR及超过5位的ENOB,展现出优异的宽带信号处理能力。本研究在大规模时间域ADC交织架构的鲁棒性优化方面提供了关键技术支撑,并为工艺演进驱动下的高可靠性高度数字化架构设计树立了新范式。

图2 芯片显微照片及面积分解

论文信息

Hongzhi Liang, Jun Chang, Yixiao Luo, Li Dang, Haolin Han, Yi Shen, Dengquan Li, Shubin Liu, Ruixue Ding, and Zhangming Zhu, "A 16× Interleaved 32-GS/s 8b Hybrid ADC With Self-Tracking Inter-Stage Gain Achieving 44.3-dB SFDR at 20.9-GHz Input," IEEE Journal of Solid-State Circuits, doi: 10.1109/JSSC.2026.3680919 (Early Access).

(来源:模拟集成电路教育部重点实验室)

4.合肥工业大学在锑基光电子器件研究中取得重要进展

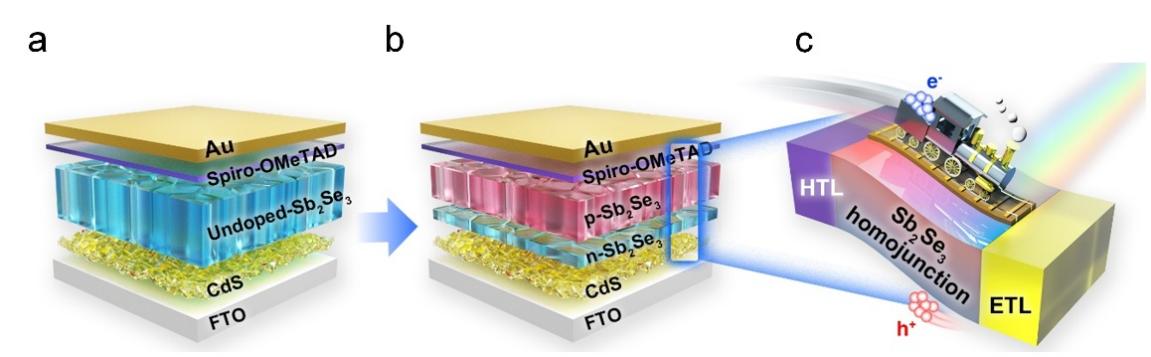

近日,合肥工业大学唐荣风教授联合中国科学技术大学陈涛教授在硒化锑(Sb2Se3)光电转换器件研究中取得新进展。研究团队围绕Sb2Se3光伏器件开路电压损失严重这一关键瓶颈问题,提出了一种基于成分调控的载流子极性控制策略,在吸收层内部构建p-n同质结结构,显著增强器件内建电场并有效抑制非辐射复合,实现了器件性能的协同提升。相关成果以“Internal Homojunction Sb2Se3 Solar Cell”为题,发表于《自然光子学》(Nature Photonics)杂志上。

Sb2Se3作为一种新兴的光吸收半导体材料,具有近理想带隙(1.1–1.3 eV)、高吸收系数以及优异的热稳定性和化学稳定性,被视为极具应用潜力的下一代光吸收层材料。然而,目前基于Sb2Se3的光伏器件效率仍显著低于CdTe、Cu(In,Ga)Se2等成熟技术,其核心瓶颈在于开路电压损失严重。这一问题主要源于器件内部内建电场较弱,难以提供足够的载流子分离驱动力;同时,吸收层体相及界面中存在大量深能级缺陷,导致严重的非辐射复合损失。

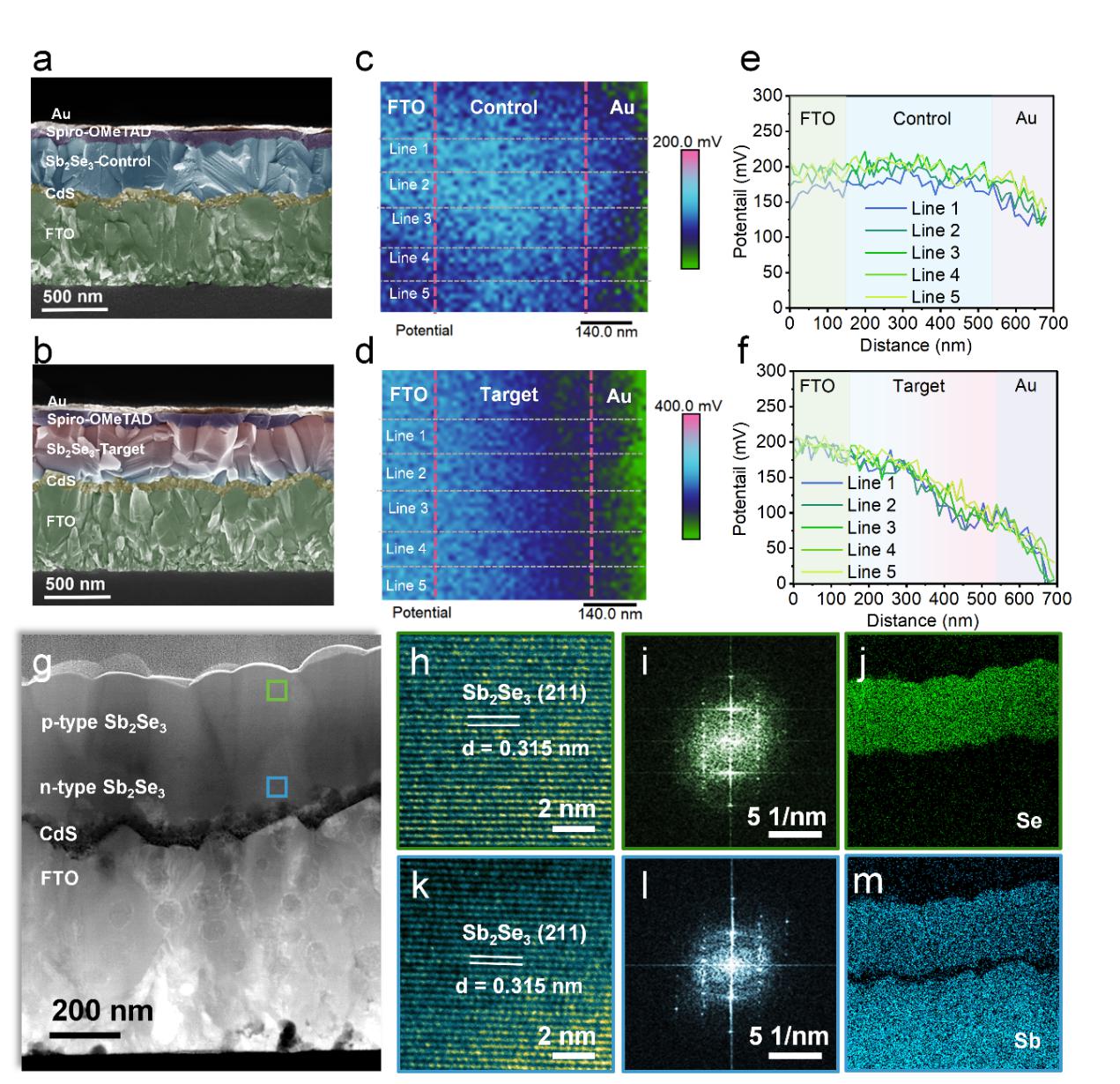

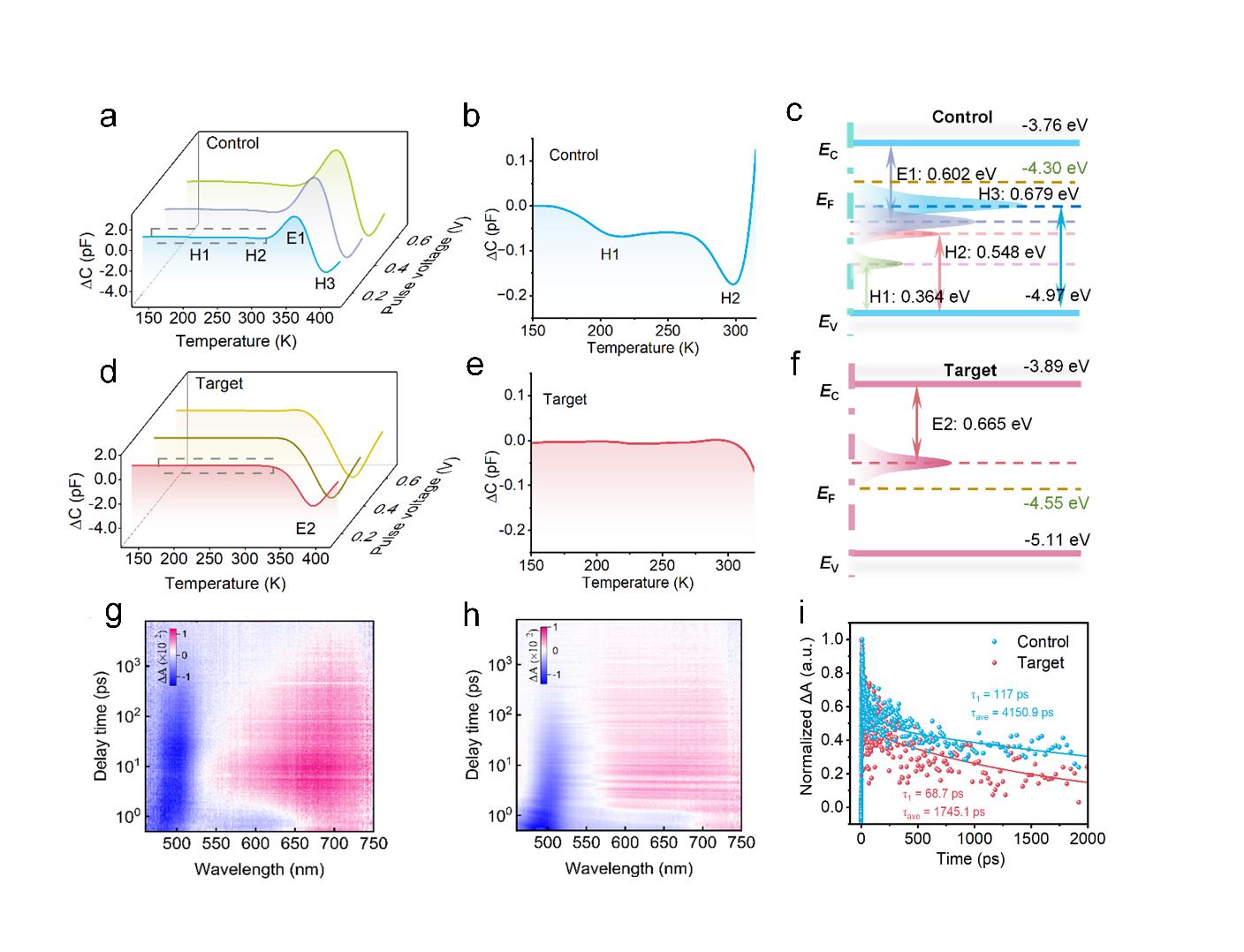

针对上述问题,研究团队提出成分驱动的本征掺杂策略,通过在热蒸发中调控Se与Sb化学势,实现薄膜导电类型在n型与p型间可控转变,载流子浓度超过1014 cm-3。采用顺序沉积法构建n/p型Sb2Se3同质结,引入额外内建电场,拓宽耗尽区,从而增强载流子分离,降低缺陷态密度,抑制非辐射复合。结合理论计算、超快光谱与深度分辨模拟等表征,证实同质结形成内建电势梯度,加速载流子传输,将复合损失降低一个数量级以上。最终制备出效率达10.15%的Sb2Se3光伏器件,开路电压损失仅0.459 V,达到该体系先进水平。该工作为降低光电器件电压损失提供了新思路,也为锑基硫族化合物光电器件的性能优化与器件设计提供了重要参考。

图1. 内置同质结Sb2Se3光电器件结构及能带示意图

图2. Sb2Se3吸收层中内建同质结的深度分辨表征

图3. Sb2Se3薄膜的DLTS缺陷分析(种类与能级)及TAS光谱表征

(来源:合肥工业大学)